在离子注入器中引入电子淋浴电流可消除GaAs外延片中由电荷引起的损伤

由LAM LUU-HENDERSON、SHIBAN TIKU、MEHRAN JANANI、JOHN BONK、STEVE CANALE和MARK BOREK来自SKYWORKS SOLUTIONS

IC行业中最复杂、持久的产量损失来源之一是电放电造成的损害。

考虑到硅行业比我们自己的行业更加成熟,毫无疑问,在硅集成电路制造中解决充电效应有着相当悠久的历史和成熟的方法论。在这些晶圆厂中,在常用于生产有源器件的离子注入步骤中,存在产量损失的潜在风险。对于某些工艺,这一步骤是在沉积介质层(如栅氧化物)之后进行的。

此外,硅晶厂可能会出现与电荷相关的产量损失,这是由于晶圆暴露在等离子体处理中造成的。在这一步骤中,紧随晶体管或电容器形成之后,由于在各种离子轰击期间积累的电放电,可能会导致有源和无源器件的损坏。

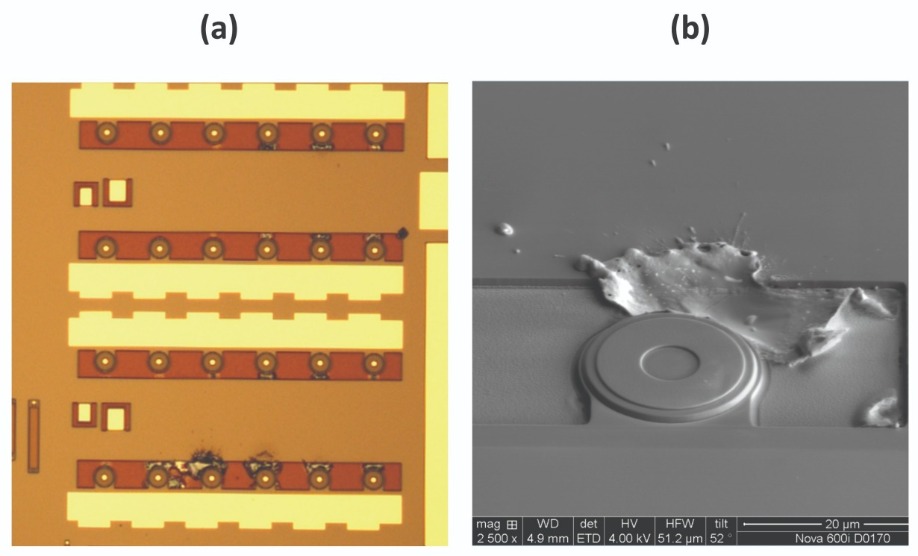

图 1. (a) Skyworks HBT 晶体管阵列试验批次上的电荷缺陷 (b) 扫描电子显微镜图像显示 HBT 结构的电荷损伤

对于从事III-V产业的人来说,相关电气放电损伤的文献要少得多,与这种产量损失机制相关的经验也更有限。因此,为了解决这一弱点,我们在Skyworks Solutions的工程团队,一家生产GaAs HEMT和HBT产品的制造商,进行了一项广泛的研究和分析。借鉴了Axcelis Technologies和Innovion Corporation的专家指导,我们探讨了植入诱导充电故障的产量影响、故障机制和可能的解决方案。

在处理III-V材料时,电气诱导缺陷的一个潜在来源是等离子体系统,因为它会在晶圆上产生高电压。为了防止产生影响可靠性的缺陷,需要采取适当的预防措施来保护晶圆。

硅集成电路行业与我们自己的行业之间一个显著的区别是,我们不在栅极下方使用氧化物或绝缘体。因此,电放电避免不是常规做法。在我们的行业中,很少生产离子注入的活性层 - 掺杂剂往往是在外延生长过程中引入的。这并不是说离子注入没有作用;它用于隔离晶片的区域。通常使用中等电流离子注入机进行此操作,但束流电流仍可能超过产生电损伤的限制。

**

**

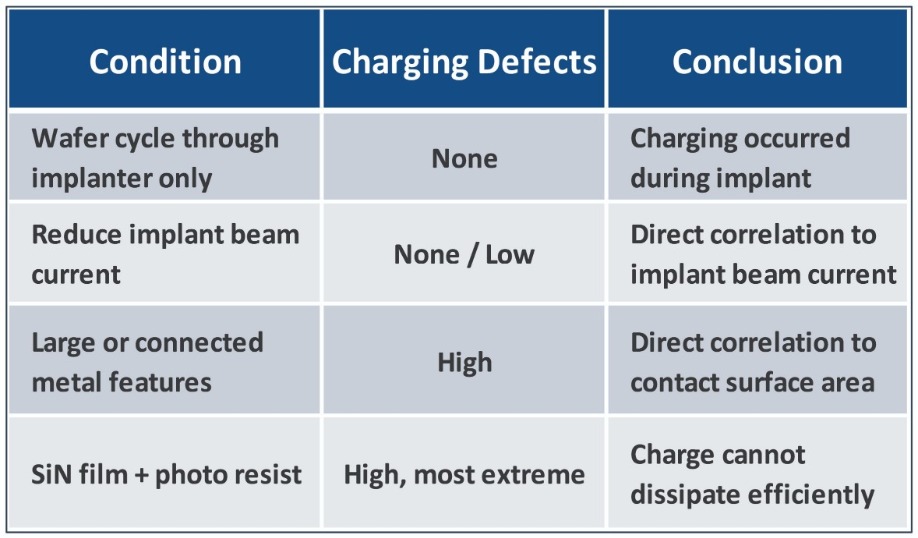

表1. 确定HBT阵列中充电缺陷起源的关键实验结果摘要。

**使用氦气工作

在我们的行业中,通常通过注入He++或He+离子来实现器件隔离。由于离子注入的固有特性,无论氦束从源到目标穿过时进行了一定程度的中和,硅片上都不可避免地会发生电荷积聚。绝缘光刻胶层和GaAs的半绝缘特性阻止了净正电荷的瞬间积聚充分耗散。这种电荷是一个问题,因为它可能导致极端的电击故障。

不幸的是,消除晶圆上设备的这种充电效应是具有挑战性的。当在离子注入之前晶圆表面有足够数量的金属接触时,这一问题尤为严重——电荷可能在这些接触处积累,并超过电气损坏的阈值。请注意,放电电流可能非常高,足以导致器件结构的熔化和破坏。

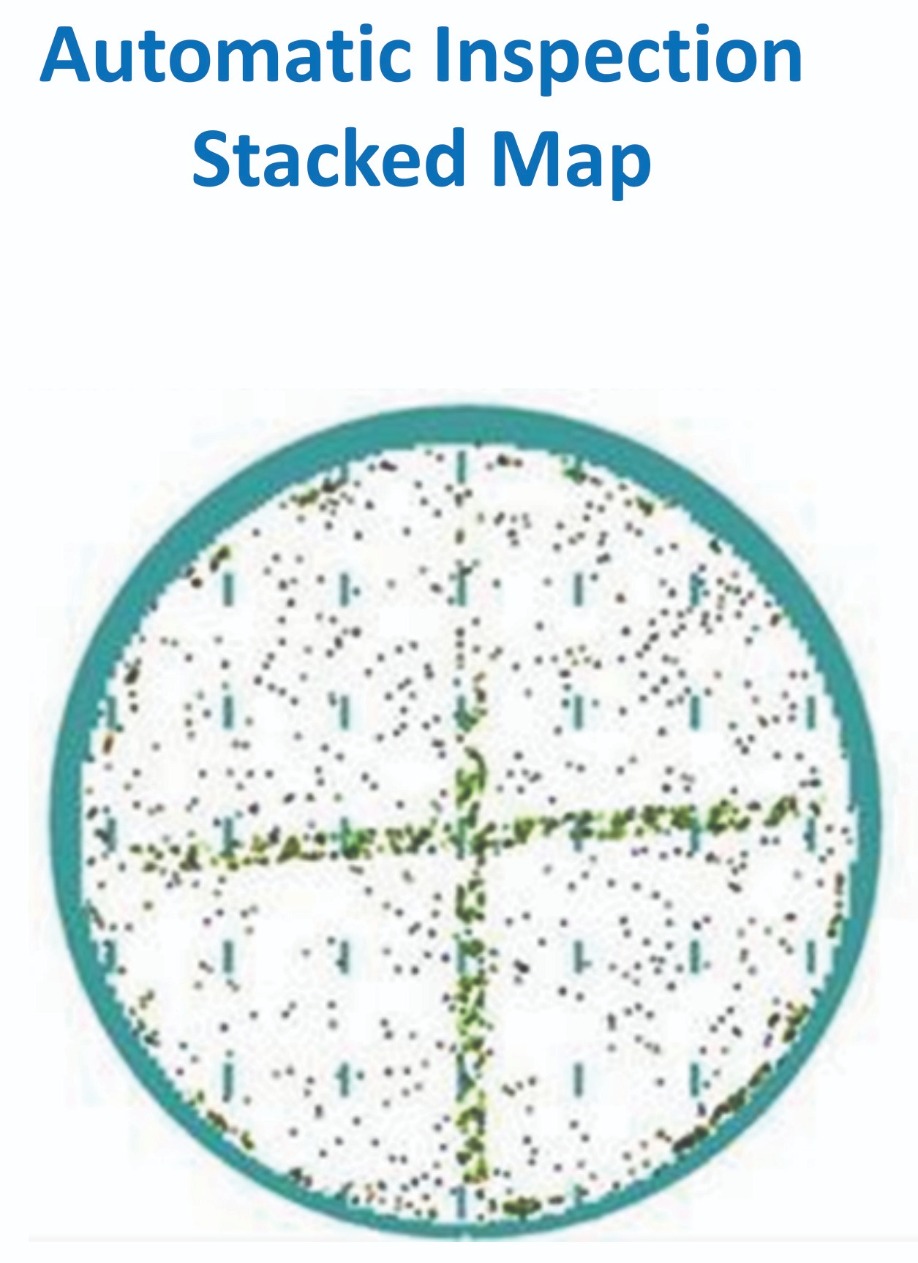

图2. 损坏芯片的堆叠式自动检测图,显示出十字准线和外环图案,带有电放电故障。

我们通过在加工流程的早期进行隔离注入工艺,来降低产量损失的可能性,因为在这一点上,晶片的表面要么没有金属接触,要么只有很少的金属接触。如果在注入之前需要金属接触,我们会采取措施来最小化严重的弧光相关损坏,比如重新排列工艺步骤。这并不罕见:为了技术进步,有时会重新排列制造流程中的工艺模块,以提高器件性能,降低成本或增加整体工艺效率。

飞行员挑战

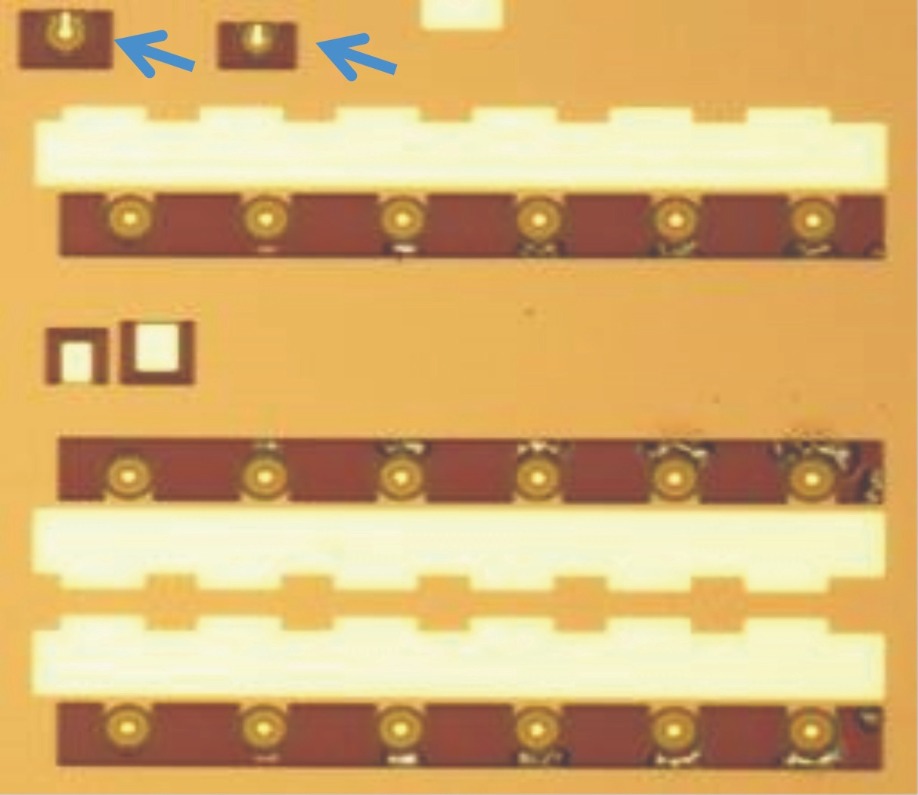

在我们最新的HBT工艺开发过程中,已经重新安排了几个步骤。在评估试验批次时,我们观察到了由严重电荷损伤引起的几个缺陷(见图1)。这些由充电引起的爆破缺陷导致了视觉和探针故障,并导致了总体产量损失约0.5%。我们的在线自动光学检测工具发现了视觉缺陷,而功能泄漏故障暴露了探针产量损失。

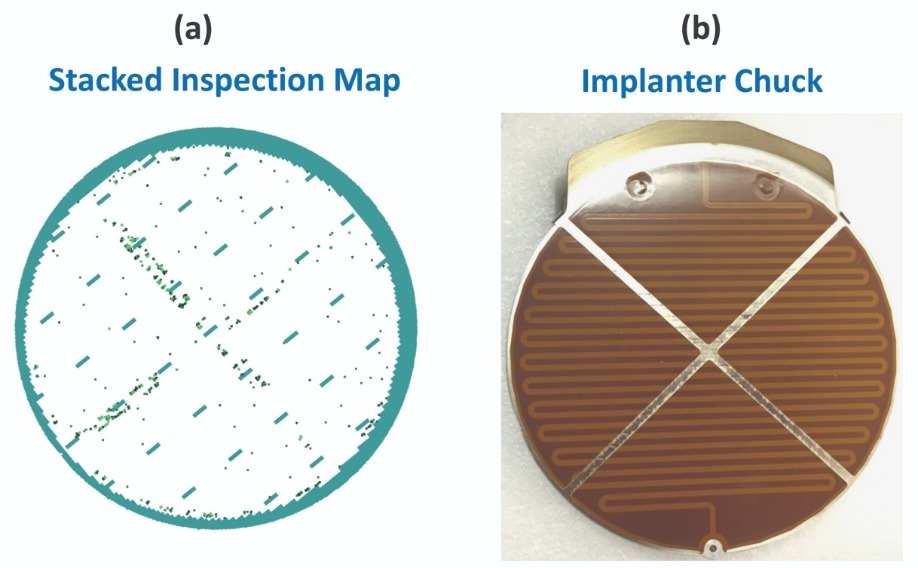

图3. (a) 受损晶片的产量图显示出电荷故障的十字交叉图案 (b) 在 Axcelis 8250 离子注入机中,静电夹具接地路径呈十字和环形图案,接地销位于夹具的左侧。

为了调查这种极端充电故障的来源,我们进行了一系列实验,评估不同类型的外延材料、光刻胶、胶厚和氮化膜密度。大多数变量对故障率影响不大。然而,这项研究揭示了损害程度与关键工艺和工具参数之间的几个强相关性,最终为这种故障机制提供了宝贵的见解。

我们的研究结果总结在表1中,包括我们观察到我们的晶片在通过注入机循环时不会出现任何电放电损伤。这意味着这些缺陷产生的电荷是在注入过程中发生的,而不是在注入机晶片站上电荷积累导致的。我们还发现,注入束电流越高,充电损伤越严重;而故障似乎高度依赖于区域,对较大的金属特征的影响要远远大于较小、孤立的特征。

另一个观察结果是,当晶片被氮化膜或光刻胶覆盖时,它们具有最严重的充电缺陷。特别容易受到这种疾病影响的是具有一层覆盖整个晶片、未图案化的光刻胶的晶片。这一观点揭示了在植入过程中积累的电荷无法被释放,这是由于介质、聚合物和半绝缘GaAs衬底的综合绝缘效应造成的。

最初,我们认为我们通过在线视觉检查发现的吹融特征是相对随机地分布在晶圆上的。但当我们叠加检查良率图时,我们发现了一个非常明显的十字和外环图案(见图2)。

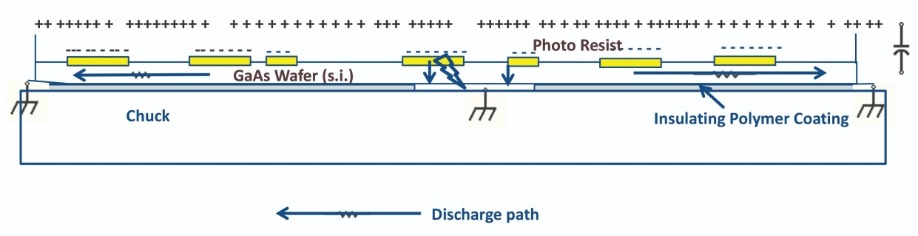

图 4. 在注入过程中晶圆上的电荷分布示意图以及通过静电夹具接地通道的耗散路径。

为了揭示这一模式的原因,我们将重点放在隔离离子注入前后的步骤上。通过仔细分割每个工艺步骤和相关工具集,我们确定离子注入是缺陷的根源。‘关键证据’是一种损伤模式,类似于我们的注入器晶圆站的十字和外环特征,该站使用静电夹持器(见图3)。

我们使用的植入机是Axcelis NV8250。我们Axcelis NV8250中的晶圆站已经经过独特设计,用于GaAs加工,夹具被分成四个相等的象限,以便每个部分的极性可以被反转,从而在晶圆植入后更好地释放晶圆。请注意,该植入机的静电夹具是对Axcelis原始夹具的修改。它旨在解决我们在原始的单外环静电夹具设计中面临的频繁晶圆断裂问题。在修改之前,由于电荷过多积聚,我们很难在植入步骤后将晶圆从夹具中分离出来,这种电荷无法迅速消散,无法使晶圆轻松释放。

通过新的夹头设计,四个部分以十字形布置在外边缘环内。通过这种布局,夹头的整个表面都涂有聚合物,除了铝十字线和外边缘环区域 - 这些是唯一通过接地销直接连接到地面的位置(见图3(b))。

图5. 电放电对HBT晶体管阵列造成损坏,但单个晶体管没有缺陷。

在植入过程中,晶片与接地引脚保持持续接触。这确保了金属接触点和晶片上积累的净电荷得到适当的释放。然而,新的工艺流程中存在金属特征。这些特征被SiN和光刻胶覆盖,两者都是绝缘体。

通过使用氮化物和光刻胶膜封装金属接触点,可以防止积聚的电荷散失。尽管这些接触点的电阻比HBT的外延层低,但外延片本身是半绝缘的;因此,释放这种电荷积累的最低电阻路径是通过接地的十字形和夹具的外环。由于这个原因,放电电流在晶圆金属特征上的浓度沿着十字形图案和外环区域增加,导致这些区域的电放电损坏概率增加。

如果它们暴露在外,晶圆上的金属特征将起到天线的作用;如果它们被光刻胶覆盖,它们会像电容器一样充电——取决于位置、大小和形状——直到电压升至临界水平,然后迅速放电到地面(请参见图4,了解此故障机制的示意图)。请注意,电阻路径取决于夹具上的位置,在十字和环形位置上最低。

随着束流电流的增加,晶圆上的电荷积累增加。这导致在注入期间接地区域周围出现电流拥挤,并随之增加更多的电击击穿故障。正如预期的那样,束流电流的大小与充电损伤的程度之间存在直接相关性。

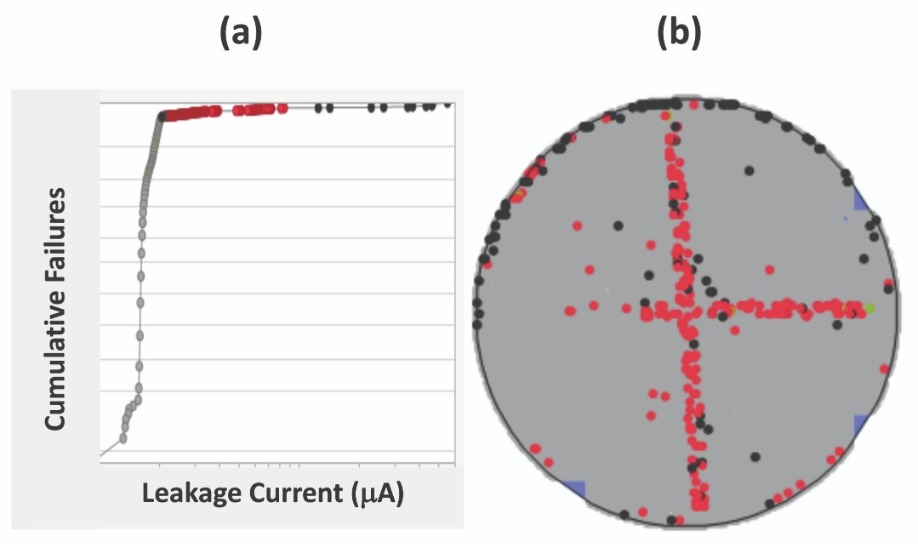

图 6 (a) 漏电测试检测到静电损坏故障的示例。 (b) 产量图显示以十字和环形图案失败的芯片。

我们对晶圆损坏原因的解释与发现一致,即故障频率取决于表面积。当金属接触面积较大时,它们会吸引并积聚更多电荷,导致更严重的电弧效应。这在光学图像中是明显的,较小的孤立晶体管不受影响,而较大的HBT阵列更容易受到电放电影响(见图5)。

请注意,对于产品晶片,金属特征通常位于光刻胶下方,其余的开放区域则被覆盖并注入。然而,在极端情况下,整个晶片可能被光刻胶覆盖,导致电荷的激增,随后发生灾难性的电荷故障。

为了有效识别这些放电故障,我们采用了两种检测模式:在植入步骤后首先进行自动光学检查,然后在最终出厂芯片检查时再次进行检查;以及泄漏探针测试。后者采用更严格的限制来捕捉电性减弱的芯片,这些芯片可能会逃过自动光学检查的检测,可能导致逃逸。为了识别这些边缘和漏电的芯片,我们增加了偏置电压(请参见图6,了解此方法的结果)。

**

**

图 7. 随着注入束流增加,充电诱导的缺陷也增加。

**生产解决方案

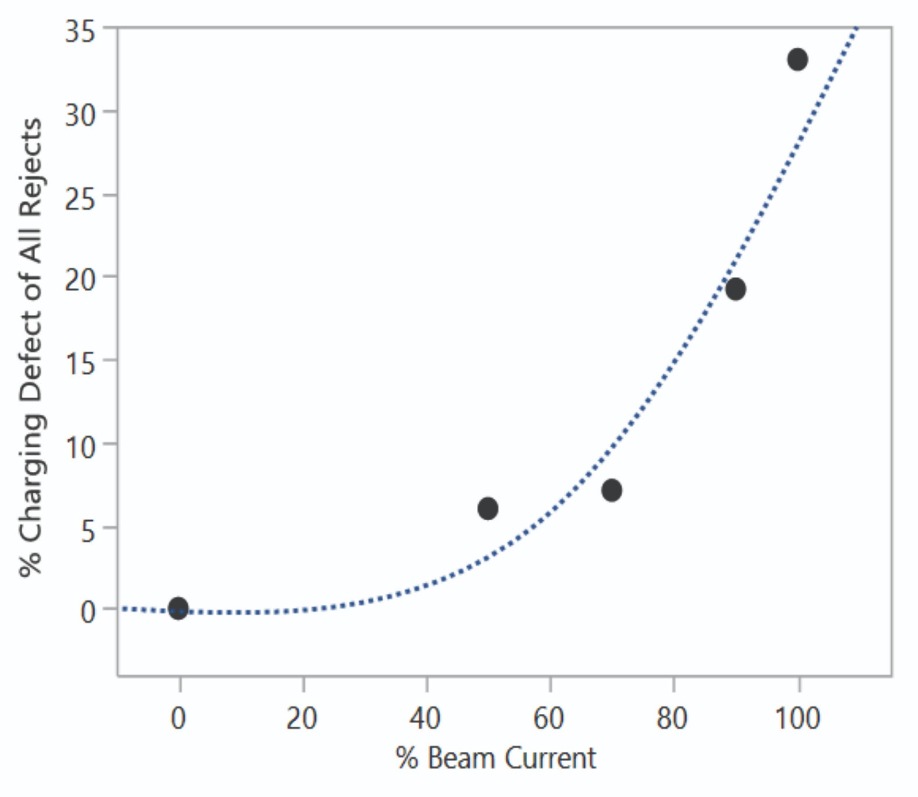

我们生活在一个精益制造的时代,在这个时代,通常不可行对每百万件零件发生的缺陷进行硬件修改。在这种情况下,需要采用替代方法来减轻和控制这类产量损失。一个选择是降低植入束流电流,以限制离子击中晶圆的速率。最终,这会减少在接触金属处收集的电荷,并应减少损坏的程度(见图7)。

为了验证这一理论,我们将植入束流电流从0%变化到100%,然后立即使用自动光学检测仔细检查植入的晶片。在比较由充电引起的故障数量与检测到的缺陷总数后,我们观察到植入束流电流与充电损伤量之间存在着强烈的相关性。

上世纪80年代,伊顿公司对植入电流对晶圆充电程度的作用进行了彻底研究和记录。他们得出了相同的结论:降低植入电流是减少由充电引起的故障数量的一种快速、简单的遏制方法。然而,这无疑会以吞吐量和整体效率的降低为代价。

图8. 通过引入电子淋浴到末端站,由于电荷诱导缺陷而减少,该站采用单丝配置。打击板由石墨制成,以避免对GaAs电路的污染。

用于Axcelis NV8250的InAir传输机器人。来源:Axcelis Technologies

Axcelis 8250的操作界面和装载站。来源:Axcelis Technologies

减少充电引起的故障的另一种选择是重新设计设备结构,以最小化电放电损坏。这种可能具有挑战性的方法涉及实施设计可制造性规则,以减少整体金属面积。通过防止任何电荷的潜在积聚,可以消除充电和静电放电故障。

这个概念对于了解硅集成电路处理中应用的“天线”规则的人来说应该很熟悉。基本原则是覆盖在晶圆上的光刻胶的面积不应超过一定阈值。然而,在进行一些电路的隔离时,比如HBT功率阵列,这可能很难实现。在这种情况下,整个阵列的长度可能达到100微米或更长,但在电气上它只是一个单一的器件,因此可以将其作为一个单一实体覆盖在光刻胶上。

遵守这些规则的一种方法是配置晶体管阵列中的集电极接触,使其在电学上仅分段(见图5)。这确保每个接触面积更小。在离子注入步骤后沉积互连金属,将接触区域连接在一起,修剪电荷积聚并降低与电弧相关事件的可能性。

用电子淋浴

在所有解决植入物充电缺陷的选项中,最可靠且推荐的是经过行业测试的电子淋浴。最初由伊顿公司开发,已被广泛应用于硅行业。

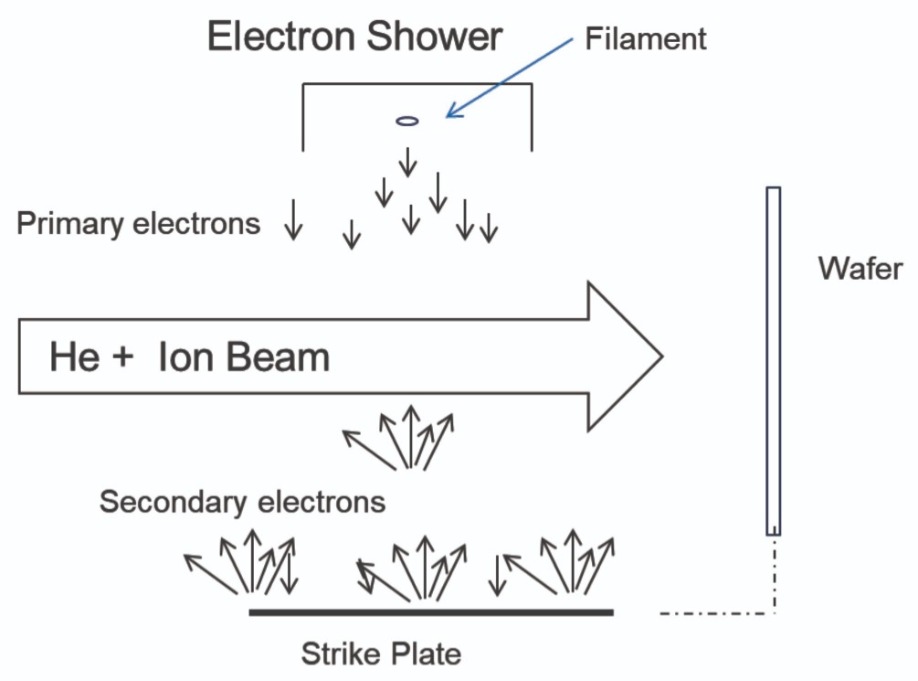

在我们的Axcelis NV8250离子注入器中,电子淋浴集成到末端站,晶圆被安置用于注入。利用这种设计,来自发射丝的电子会向离子束涌入大量负电荷,中和正的He+和He++离子,以便注入前(见图8)。

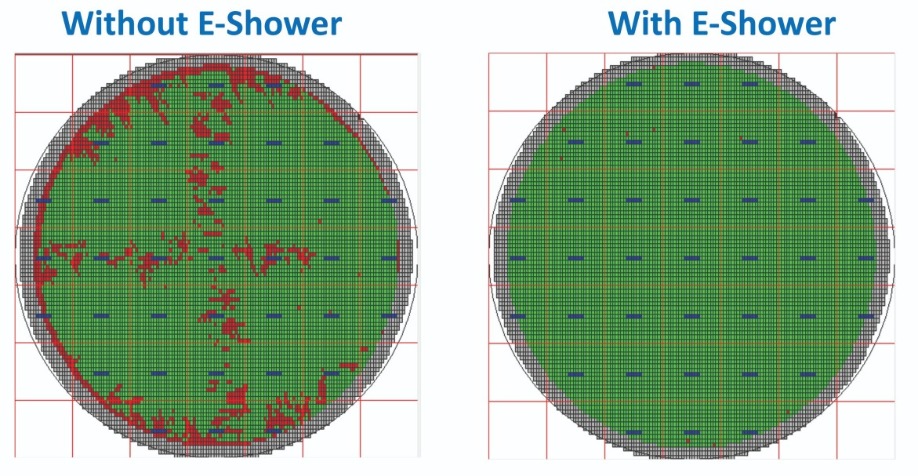

图 9. 在隔离注入过程中,带有和不带有电子淋浴的晶圆产量图。

使用我们的工具,静电卡盘在注入之前将晶圆水平固定。然而,一旦离子束被优化用于注入,该卡盘终端站将移动到竖直位置。当初级电子击中打击板时,会产生次级电子,确保正电荷不会积聚。此外,当束击中晶圆表面时也会产生次级电子(见图8)。

许多高产量、高密度的集成电路工厂使用带有电子淋浴的工具。这是一种可靠的技术,但也存在风险,因为可能会出现来自负电位的充电缺陷。因此,在优化电子淋浴设置时,避免由于负电荷过量而产生放电损坏,需要进行谨慎的工艺开发。工程师必须在确保中和和防止过多负电荷之间保持微妙的平衡。

为确定最佳的电子束设置,我们进行了一项'实验设计'。这涉及用接触金属沉积并涂覆SiN的GaAs晶片,以及带有无图案隔离光刻胶的晶片,这为评估充电损伤程度提供了极端条件。这两种类型的晶片均进行了带有和不带有电子束的注入。实验表明,经过电子束处理的晶片没有充电症状,而没有电子束的晶片出现了严重的放电损伤(见图9)。

图10. 充电引起的缺陷百分比随电子束原始束流的变化,对于给定的注入配方。

请注意,我们使用的中电流注入器具有灵活性。我们可以使用多达三根丝,但建议只使用一根或两根,只要这样就能提供足够的中和。在我们的评估中,我们使用了一根丝。

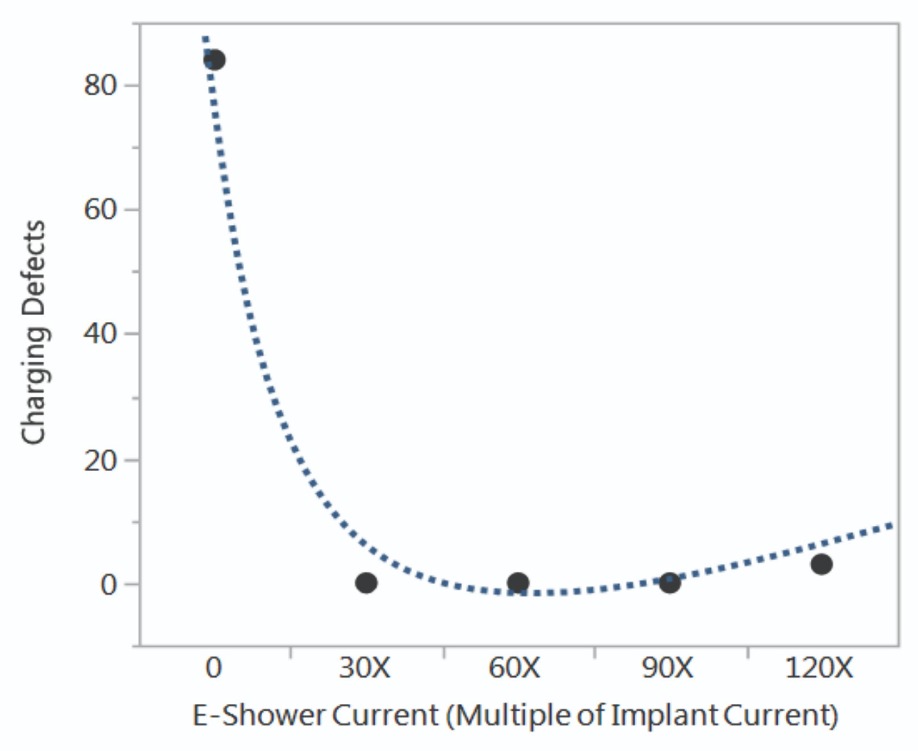

建议电子淋浴主电流应该是植入束电流的约三十倍。我们已经对这一数字进行了测试,发现即使电流远远超过这个建议值,仍然没有植入充电诱发的缺陷(见图10)。换句话说,使用 Axcelis NV8250 有一个非常宽广的工艺窗口,同时实现了极低的负充电概率。

通过进行多次设计实验的迭代,我们已确定了 Axcelis NV8250 注入机的理想电子束过程条件。这进一步改善了最佳隔离和循环时间,以及显著提高了电荷产量损失。

我们的工作表明,电荷和由此造成的损害不仅限于硅集成电路行业,而且还延伸到基于集成电路的制造商

III-V族化合物。充电可能发生在涉及等离子体或电荷束的所有工艺步骤中。特别是,故障可能可以追溯到在隔离过程中使用的离子注入步骤,该步骤有可能对金属特征造成严重的可见损坏。如果更改处理顺序,或者修改涉及电荷物种的工艺步骤,存在这样的威胁,即这种新例程会产生可见或光学上无法检测的缺陷。

在我们的情况下,我们的新流程涉及覆盖具有现有金属特征的半绝缘晶片,然后进行离子注入步骤之前用绝缘SiN和光刻胶覆盖。不幸的是,这种组合创造了灾难性电放电产生的理想条件。为了彻底解决这个问题,并最终确定最佳前进方式,我们进行了对这些植入引起的故障的详细评估,随后进行了彻底的实验分析。随后的发现使我们能够揭示主要的故障机制,并打开了关键的预防方法、适当的质量控制措施以及产品产量和可靠性的整体改进之门。